Hi Quadman.

Great to hear you got your DIYinHK board all safe and sound.

Yeah, you want that card reasonably secure, the pin connections won't like

being moved round too much. Though they will probably like a gentle re-insertion

every 3 months or so, as most pressure based connections do.

Good luck ... let me know if you run into any issues. I want to hear that report

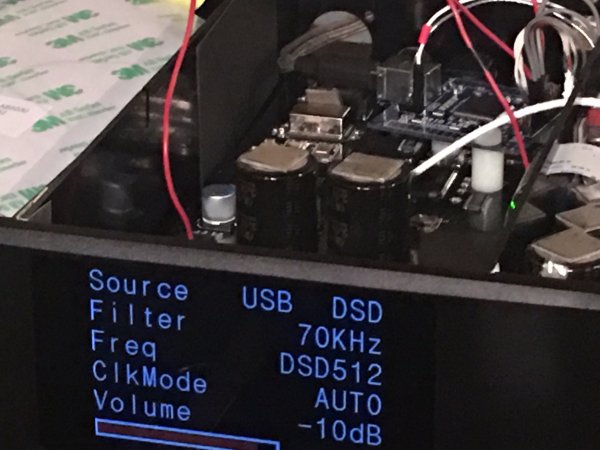

on the differences between DSD 256 & 512 !!

Anyway, I'm currently stuck in a very dull hotel room, and was just thinking about that

coax linking the two X20 boards. One of the questions that struck me, was what is it actually

transmitting ?

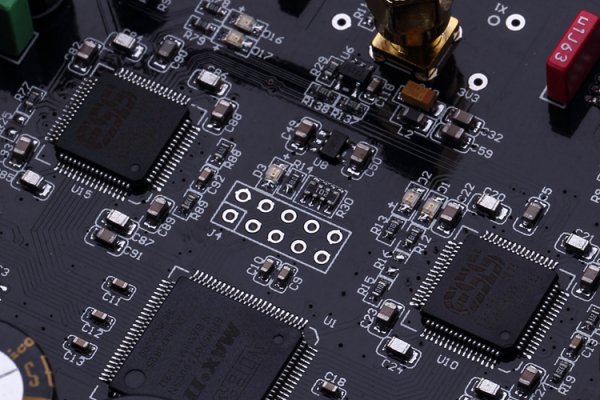

Looking at the ess9018 spec sheet, it has the usual I2S inputs of BCLK, MCLK, LRCK & DATA (8 channels)

With all the clocks and processing stuff etc being on the digital board, I kind of very vaguely thought

that somehow all the important stuff? was being mixed into a special stream by that main FPGA,

then sent over to the smaller FPGA on the output board through this imposing connection,

before being reconstituted into the relevant streams prior to being sent to the DAC chips?

Now, after actually thinking about it, I realise of course that it's simply the system master clock.

With the actual I2S channels being fed by the LVDS chips and lines that go between the boards on

that exposed white ribbon cable.

This would then be similar-ish to how the LKS DAC sends it's I2S information round it's rather large PCB.

The LKS however, places it's master clock very close to the ESS chips, just about where the coax terminates

on the X20.

The more I think about it, the more this makes sense to me.

However, my digital knowledge is pretty ropey (as you can tell from the misapprehension stated

above) and I'm really just picking this stuff up as I go along.

I'm away at the moment, but will check all this out when I get back. It does mean

that what I foolishly thought was basically just a ribbon containing system control stuff.

Is actually the main I2S data lines. So, be careful with it, and don't kink it etc when

handling. It also looks rather exposed to me now, and I may try a bit of sheilding to see

if that improves the sound.

It also means that even if you go directly into the PCIe slot, the signal still ends up

going through an LVDS network (just like the HDMI input), and gets a double dose if you

actually use the HDMI port. Not terrible by any means, and a pretty common thing to do, but

one of the many compromises that manufacturers have to make when designing this type

of product. I found going from HDMI to using the PCIe slot a step up in quality, which shows

the effect using these circuits can have.

I'm now assuming that the smaller FPGA chip on the output side simply divides the relevant

signals between left and right DAC chips, rather than anything fancy. The main large FPGA on

the digital board handling input selection and any re-clocking stuff.

It's a real pity there are no standard I2S pins on the output board. However, even by going

the LVDS route (like the Audiophonics card) there is the intriguing possibility of maybe adding

a high quality clock signal direct into the coax socket (I've already seen this done, and

wondered about it, on a Chinese site) and inputing an I2S LVDS signal direct into the

output board from something like the WaveIO. Completely bypassing the Gustards digital

section. No need for any input selection of course, the only thing that may cause trouble

might be lack of volume control, but going Rics modified output route, you wouldn't need it

anyway, and I only really use it to tame the X20's ridiculously high output.

Intriguing stuff to ponder, and probably all wishful thinking on my part. Lol ...

I'm going to have to read up about clocks now ... I've regularly seen users swap out their

clocks on other DAC's for various different brands. The LKS even has dedicated input pins

right by the standard clock for an external 100mhz clock. So, this isn't just another of

my crazy ideas. I'm not sure that DSD is even clocked in the same way as PCM. And, since

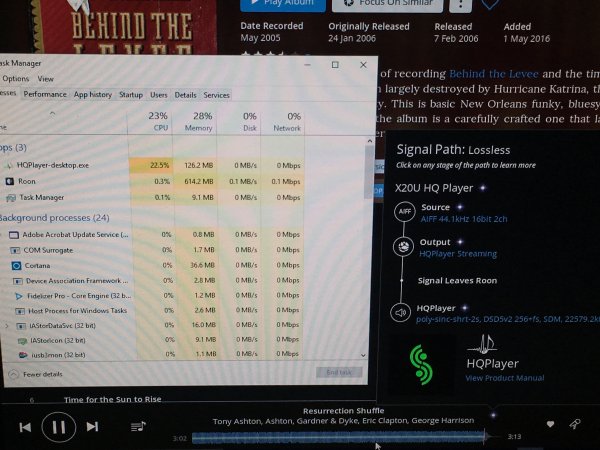

the conversion clocks on the WaveIO are at least as good as the ones in the Gustard, what

do I need the re-clocking that the FPGA is possibly doing for?

Lots of questions, but no answers as yet. However, the spectre of future experimentation

has just reared it's ugly head ...

Regards

Simon