Not an argument, at all. Merely re-stating what many seem to miss. Wish I had a dollar, for every time someone insisted they have a 75R RCA. That story got old. Around 20 years ago. How certain firms seem to be able to perpetrate this myth baffles me.

Reflections and DACs

- Thread starter DonH50

- Start date

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Whats your take on XLR compared to BNC?

So many engineers have commented on RCA in the past I try to avoid it like the plague, but I find in audiophile world it is easier to get XLR orientated products than the BNC in general (ignoring the minority of quality pro-audiophile manufacturers).

Thanks

Orb

So many engineers have commented on RCA in the past I try to avoid it like the plague, but I find in audiophile world it is easier to get XLR orientated products than the BNC in general (ignoring the minority of quality pro-audiophile manufacturers).

Thanks

Orb

Good question!

XLR connectors actually do measure 110R. However, there is a large discontinuity, in most of them, that doesn't look very good, when measured on the high-$ equipment, one would use to make such determinations. Some of that can be fixed with zobel networks. How important that is, and if it is really audible, remains open to debate. I guess if one wants the best, then work needs to be done. Not impossible, but requires a fair amount of expertise.

Where things get interesting...................the cables...............

Several of the big name AES/EBU cables (you know, the ones you would buy in bulk, from any number of suppliers) do not measure 110R. Despite claims to such, in the data sheets. I am not going to name brands, but some of them work much better as USB cables, than AES/EBU cables. (Yes, this has been verified by both measurements and listening tests. No, they were not DBT. Sorry!)

And some USB cables work better as AES/EBU. (Yes, same disclaimer.)

XLR connectors actually do measure 110R. However, there is a large discontinuity, in most of them, that doesn't look very good, when measured on the high-$ equipment, one would use to make such determinations. Some of that can be fixed with zobel networks. How important that is, and if it is really audible, remains open to debate. I guess if one wants the best, then work needs to be done. Not impossible, but requires a fair amount of expertise.

Where things get interesting...................the cables...............

Several of the big name AES/EBU cables (you know, the ones you would buy in bulk, from any number of suppliers) do not measure 110R. Despite claims to such, in the data sheets. I am not going to name brands, but some of them work much better as USB cables, than AES/EBU cables. (Yes, this has been verified by both measurements and listening tests. No, they were not DBT. Sorry!)

And some USB cables work better as AES/EBU. (Yes, same disclaimer.)

How did we get onto connectors? In any event, an XLR is designed for balanced audio-frequency signals, while BNC for controlled-impedance single-ended (relatively low-frequency, though there are exceptions) RF systems. They are not terribly comparable in performance and target very different applications. This thread started off looking at DAC clock signals, not the audio signals at the output. I have never seen a S/PDIF XLR, and have never personally (as far as I can recollect) measured the impedance of an XLR connector.

XLR and BNC both offer more positive capture than RCAs, though BNC is better. SMA (SMB, 3.5 mm, 2.92 mm, K, etc.) are much better, and their performance and cost reflect that.

Audio interconnects get away with RCA analog plugs because impedance-matching is considered unimportant at the frequencies and impedances involved (that debate goes on). And, they are cheap! As a connector for an RF signal, eh, I think they su** -- uh, are poor performers.

XLR and BNC both offer more positive capture than RCAs, though BNC is better. SMA (SMB, 3.5 mm, 2.92 mm, K, etc.) are much better, and their performance and cost reflect that.

Audio interconnects get away with RCA analog plugs because impedance-matching is considered unimportant at the frequencies and impedances involved (that debate goes on). And, they are cheap! As a connector for an RF signal, eh, I think they su** -- uh, are poor performers.

Well...........

Our good buddies, at the AES, thought it would be a good idea, to use the same connector for digital signals, as audio signals. I tried to tell them, but no one listened. Ironic part is they realized their initial iteration was a bad idea. So, it was modified. It went from horrible to workable, but still bad. Unfortunately, we are stuck with it. Just as we are with SPDIF.

AES/EBU seems to be the flavor-of-the-month, this year, for digital interconnects.

Sorry for the interruption..............back to you, Don.

Our good buddies, at the AES, thought it would be a good idea, to use the same connector for digital signals, as audio signals. I tried to tell them, but no one listened. Ironic part is they realized their initial iteration was a bad idea. So, it was modified. It went from horrible to workable, but still bad. Unfortunately, we are stuck with it. Just as we are with SPDIF.

AES/EBU seems to be the flavor-of-the-month, this year, for digital interconnects.

Sorry for the interruption..............back to you, Don.

Oops, should have said "no consumer XLR digital cables".

No worries, appreciate your insights! - Don

p.s. 110R = 110 ohms characteristic impedance? I am not used to seeing that nomenclature, sorry. I would not have guessed XLR comes out at 110 ohms (differential, I assume?)

No worries, appreciate your insights! - Don

p.s. 110R = 110 ohms characteristic impedance? I am not used to seeing that nomenclature, sorry. I would not have guessed XLR comes out at 110 ohms (differential, I assume?)

That is correct. However.................

If you look at some of the data sheets, for 110R cable, they don't measure them in the manner that we use them. They do measure differentially, but connect the shield to one of the conductors. Which ruins what balanced/differential is supposed to be all about.

Also explains why some cables measure at the wrong impedance. Once you connect the shield to one of the conductors, you add capacitance, which lowers the Z. At that point, the Z measures properly. As I said, too bad no one connects them in that manner.

Well, I hope they don't!

The cables we have measured to have the correct impedance are the ones which sound best, when hooked up differentially, and the shield goes to pin 1.

Doesn't explain the ones that measure low, when the shield is not connected.

If you look at some of the data sheets, for 110R cable, they don't measure them in the manner that we use them. They do measure differentially, but connect the shield to one of the conductors. Which ruins what balanced/differential is supposed to be all about.

Also explains why some cables measure at the wrong impedance. Once you connect the shield to one of the conductors, you add capacitance, which lowers the Z. At that point, the Z measures properly. As I said, too bad no one connects them in that manner.

Well, I hope they don't!

The cables we have measured to have the correct impedance are the ones which sound best, when hooked up differentially, and the shield goes to pin 1.

Doesn't explain the ones that measure low, when the shield is not connected.

Using/measuring a balanced cable single-endedly with the shield connected that way does not make much sense to me but whatever... I would measure each to shield, then differentially, but as I said my experience is more RF in nature (differential stripline/microstrip/CPW lines).

You mean you have measured cables that have lower Z in balanced configuration with the shield not connected, than when it is? You connect the shield, and the impedance goes up? Have to think on that... Implies common-mode impedance is lower than differential, I think. For balanced measurements, do you use a four-port VNA, or something else?

Curious - Don

You mean you have measured cables that have lower Z in balanced configuration with the shield not connected, than when it is? You connect the shield, and the impedance goes up? Have to think on that... Implies common-mode impedance is lower than differential, I think. For balanced measurements, do you use a four-port VNA, or something else?

Curious - Don

Oops, should have said "no consumer XLR digital cables".

No worries, appreciate your insights! - Don

p.s. 110R = 110 ohms characteristic impedance? I am not used to seeing that nomenclature, sorry. I would not have guessed XLR comes out at 110 ohms (differential, I assume?)

Yes I was referring to the digital interface-cable XLR

I should had said AES3 I agree to avoid confusion with the analogue.

Thanks for the good responses from both of you, very interesting posts on it.

Cheers

Orb

As a complete non-techie who just enjoys listening and learning some of the more day to day practical applications of what you all have been discussing...what is your view on i2s connection? My DAC accepts it, and the matching transport which i am contemplating buying does have a proprietary i2s configured for the DAC. thanks for your advice.

What little I know about I2S I stated in the Rock Around the Clock thread. Here's what I said there:

My opinion now is the same -- I think a manufacturer willing to use a relatively little-known (in the consumer world) standard and run a separate clock connector is more likely to produce a better design. Sort of like high-end CDs -- data format is the same, and I seriously doubt adding gold or whatever really makes much difference in the bit stream, but more care in mastering can make them sound better. But of course it could be all marketing hype.

Finally, I know almost nothing about I2S. Separating the clock could help, but of course it depends on how well the clock is implemented. I would guess anybody going to the trouble of running extra lines and connectors will probably do a good job since it's likely to be found on higher-end gear. The clock recovered (de-embedded, if you want to think of it that way) from a data stream can be extremely good, however. Like anything else, it comes down to how good the recovery circuits are.

My opinion now is the same -- I think a manufacturer willing to use a relatively little-known (in the consumer world) standard and run a separate clock connector is more likely to produce a better design. Sort of like high-end CDs -- data format is the same, and I seriously doubt adding gold or whatever really makes much difference in the bit stream, but more care in mastering can make them sound better. But of course it could be all marketing hype.

Yes I was referring to the digital interface-cable XLR

I should had said AES3 I agree to avoid confusion with the analogue.

Thanks for the good responses from both of you, very interesting posts on it.

Cheers

Orb

A balanced cable with better capture (assuming a Neutrik or similar plug/jack pair) and reasonable impedance should provide greater noise immunity, lower loss, etc. As always, it will end up depending upon how good the transmitters/receivers are. Again, one (well, I) would hope those willing to go the extra mile with the connectors, pro or consumer gear, are also putting a little more into the circuits behind them.

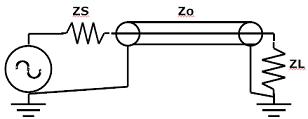

While looking over this, I realized I never got back on a question about voltages along the line and at the ends (source and load). Here are a couple of quick pictures that might help...

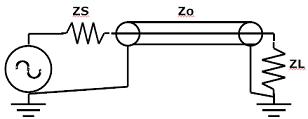

First, the test system. This is a very simple test, just an ideal source with real (resistor) output impedance, a transmission line, and resistor load. For this example, the source and transmission line impedances are both 100 ohms, and we'll vary the load. The source outputs a 100 ns pulse 2 V high. These are arbitrary, just making life easy. The transmission line is 20 ns long (about 9.5 feet for the parameters I plugged in; again, immaterial to this post).

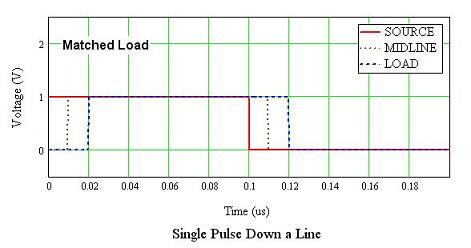

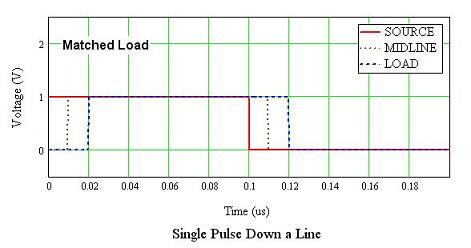

This first picture is with a matched load (ZL = 100 ohms). The source pulse (solid red line) starts at zero and ends at 100 ns as expected. At the transmission line (SOURCE), the voltage is divided by two since half the voltage is dropped across the source resistor, and the other half across the transmission line. At the middle of the line, the pulse (MIDLINE, dotted brown) rises to 1 V 10 ns after the start of the pulse as expected. This is the travel time for the pulse from the source to reach the middle of the line. The load (LOAD, dashed blue) sees the start of the pulse 10 ns later, or 20 ns from the time the source pulse first hit the transmission line. Since everything is perfectly matched, there are no reflections, and the pulse dies away cleanly.

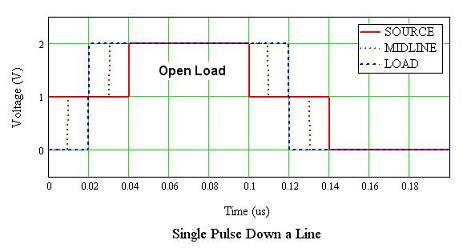

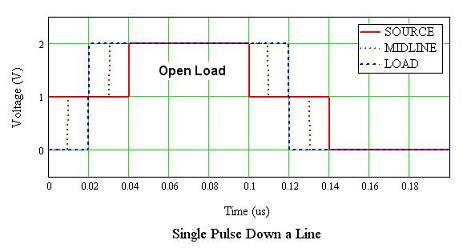

Now, to take an extreme case, what happens if the load is open (infinite ohms)? Now, starting out there is a voltage divider with the transmission line as before, but when the pulse hits the end of the line (at 20 ns) there is nowhere for the extra current to go (no load), and the voltage steps up to the open-circuit voltage, 2 V. Wow, twice the voltage! Not twice the power, however, conservation of energy and all that, and since the load cannot absorb any energy (it is an open), the pulse is reflected back toward the source.

Now, 20 ns later, or 40 ns after the starting edge, the reflected pulse from the load hits the source end of the line. This now doubles the voltage at the source end, stepping up to 2 V (1 V from the source plus 1 V from the reflected wave). At 100 ns, the source turns off, and the voltage drops to 1 V, all from the reflected wave. Then 40 ns after that, all the initial pulse has traveled to the load and back, and the system is back at 0 V.

Now, if this was a real system, with a real clock signal (pulse train), complex impedances, and no perfect matching anywhere, you could end up with a very complicated plot, with all sorts of ripples and different edges at different times from all the different reflected waves running around. The signal at any given time is a function of current (that is, present-time) and previous signals, the length of the line, and all the different impedances (source, line, load, including connectors and whatnot). That sort of thing can cause sampling errors because the clock no longer has single, clean edges during each cycle.

No wonder buffering and re-clocking with a known-good clock signal is so popular!

Hope this helps - Don

First, the test system. This is a very simple test, just an ideal source with real (resistor) output impedance, a transmission line, and resistor load. For this example, the source and transmission line impedances are both 100 ohms, and we'll vary the load. The source outputs a 100 ns pulse 2 V high. These are arbitrary, just making life easy. The transmission line is 20 ns long (about 9.5 feet for the parameters I plugged in; again, immaterial to this post).

This first picture is with a matched load (ZL = 100 ohms). The source pulse (solid red line) starts at zero and ends at 100 ns as expected. At the transmission line (SOURCE), the voltage is divided by two since half the voltage is dropped across the source resistor, and the other half across the transmission line. At the middle of the line, the pulse (MIDLINE, dotted brown) rises to 1 V 10 ns after the start of the pulse as expected. This is the travel time for the pulse from the source to reach the middle of the line. The load (LOAD, dashed blue) sees the start of the pulse 10 ns later, or 20 ns from the time the source pulse first hit the transmission line. Since everything is perfectly matched, there are no reflections, and the pulse dies away cleanly.

Now, to take an extreme case, what happens if the load is open (infinite ohms)? Now, starting out there is a voltage divider with the transmission line as before, but when the pulse hits the end of the line (at 20 ns) there is nowhere for the extra current to go (no load), and the voltage steps up to the open-circuit voltage, 2 V. Wow, twice the voltage! Not twice the power, however, conservation of energy and all that, and since the load cannot absorb any energy (it is an open), the pulse is reflected back toward the source.

Now, 20 ns later, or 40 ns after the starting edge, the reflected pulse from the load hits the source end of the line. This now doubles the voltage at the source end, stepping up to 2 V (1 V from the source plus 1 V from the reflected wave). At 100 ns, the source turns off, and the voltage drops to 1 V, all from the reflected wave. Then 40 ns after that, all the initial pulse has traveled to the load and back, and the system is back at 0 V.

Now, if this was a real system, with a real clock signal (pulse train), complex impedances, and no perfect matching anywhere, you could end up with a very complicated plot, with all sorts of ripples and different edges at different times from all the different reflected waves running around. The signal at any given time is a function of current (that is, present-time) and previous signals, the length of the line, and all the different impedances (source, line, load, including connectors and whatnot). That sort of thing can cause sampling errors because the clock no longer has single, clean edges during each cycle.

No wonder buffering and re-clocking with a known-good clock signal is so popular!

Hope this helps - Don

You mean you have measured cables that have lower Z in balanced configuration with the shield not connected, than when it is? You connect the shield, and the impedance goes up? Have to think on that... Implies common-mode impedance is lower than differential, I think. For balanced measurements, do you use a four-port VNA, or something else?

Curious - Don

Maybe I was not clear enough..........sorry..........

Simply put, if you connect the shield to one of the twisted pair wires, it adds capacitance. Which lowers Z. (Look up pretty much any Belden twisted pair: they give pF/ft values, for both configurations. The screwy one has more capacitance.)

I use a conventional TDR. Usually, I can measure Z, w/o a termination. Allows using the cursor to give a direct Z reading. Assuming the cable is short, and not lossy. Once I find something of interest, I hook it to a transformer, and terminate the far end, in the previously measured value, just to make sure. (Can not use a transformer, and the cursor, to read Z. The cursor is strictly a voltage level reading, and the transformer acts like a low Z load, so it screws up the cursor.)

OK, that makes sense. Whew! -- I was going to have to review common-mode and differential impedance with my old mW EM theory book, and I was not looking forward to that.

I still use a TDR for boards, but the chips have gotten so small these days a TDR doesn't help all that much (traces too short and too lossy for any practical TDR to resolve; I have used some <ps models but they are a PITA and cost a fortune). I have a dream of retiring and picking up bunch of test gear to play around with audio stuff again. Actually, I have a dream of just retiring...

Thanks - Don

I still use a TDR for boards, but the chips have gotten so small these days a TDR doesn't help all that much (traces too short and too lossy for any practical TDR to resolve; I have used some <ps models but they are a PITA and cost a fortune). I have a dream of retiring and picking up bunch of test gear to play around with audio stuff again. Actually, I have a dream of just retiring...

Thanks - Don

You actually have books that 'splain all this stuff? I'm impressed. Nothing, repeat, nothing I was exposed to in college prepared me for any of this. I was dropped in front of a microwave link analyzer, and told to fix the group delay problem, on the IF pre-amp. Yep, 100% OJT, or ham radio learnin'.

The only decent book I have is Matthys' book on oscillators.

The only decent book I have is Matthys' book on oscillators.

Grad school. But, like you, the good stuff is OJT (or in obscure, very good, very hard to find, veryexpensive books written by the people who did the work!)

The original post is superb - the best explanation that I've read so far.

As Don says, its not a new idea, but a good presentation. When I was first learning about jitter five years ago, it was probably Steve Nugent of Empirical Audio who made the light click for me at the end of this thread:

http://www.audiocircle.com/index.php?topic=31754.40

Steve wrote this well-known piece in PFO:

http://www.positive-feedback.com/Issue14/spdif.htm

As Don says, its not a new idea, but a good presentation. When I was first learning about jitter five years ago, it was probably Steve Nugent of Empirical Audio who made the light click for me at the end of this thread:

http://www.audiocircle.com/index.php?topic=31754.40

Steve wrote this well-known piece in PFO:

http://www.positive-feedback.com/Issue14/spdif.htm

I wince when I read something like this: it's full of pseudo-science and twisted ideas that may still lead to a good outcome, by luck more than anything else, but it throws a lot of a baggage into the arena which is quite unnecessary, and makes it harder to convince people to use good engineering solutions.

Frank

Similar threads

- Replies

- 20

- Views

- 1K

- Replies

- 5

- Views

- 623

- Replies

- 11

- Views

- 966

Members online

- agencal

- Republicoftexas69

- abaudio10

- emoonie

- conoid

- drrsutliff

- NeilB4me

- dminches

- DMSB

- Don Reid

- Audio Addict

- TooCool4

- Tuckia

- Andrew K

- jazzdude99

- the sound of Tao

- RyanTX

- JeremyMTB

- pattad

- pt999

- keithc

- Adelmor

- hairyderriere

- DennisH

- joaovieira

- KeithR

- vindixon

- Mike Lavigne

- moby2004

- Gregadd

- John T

- vinyl_mike

- cjfrbw

- roadCingKlassik

- kyoya78

- AudioLibertarian

- tony22

- gds7368

- Ron Resnick

- cdka

- Kris

- Raidersfan

- Tapetech

- barbz127

- DLS

- MarkusBarkus

- MusicLoverUpstateNY

- Lakegolf

- Solotov

- audiom3

Total: 962 (members: 66, guests: 896)

| Steve Williams Site Founder | Site Owner | Administrator | Ron Resnick Site Co-Owner | Administrator | Julian (The Fixer) Website Build | Marketing Managersing |